[ASICs] [Chip Typen] [Chip Aufbau] [

Entwicklung] [Schnittstellen] [Glossar]

[Modellierung] [Strategie] [Synthese] [ASIC Test] [VHDL-Kurs] [Beispiel]

Wie entwickelt man ein ASIC?

Wie entwickelt man ein ASIC?

Am Ende einer ASIC Entwicklung steht ein Chip mit der integrierten Schaltung - so viel steht schon einmal fest. Aber wie geht's los und was macht man unterwegs um dorthin zu gelangen? Welche Werkzeuge werden dafür benutzt?

Um den Weg eines ASIC's vom Anfang bis zum Ende so verständlich wie möglich zu beschreiben, möchte ich den gesamten Entwicklungsweg in verschiedene Phasen aufteilen. In diesen Phasen bewegt man sich auf unterschiedlichen Ebenen und benutzt darin entsprechende Werkzeuge. Bei den Werkzeugen handelt es sich ausschließlich um CAD Software (Computer Aided Design). Dieses besagt indirekt, daß bis zur Fertigung des ASICs alle Phasen bis auf die eigentliche Produktion am Ende in oder mit einem Computer durchlaufen werden. Alle Zwischenprodukte sind rein `elektronisch´ und liegen nur als Dateien vor. Um den Entwicklungsprozeß zu verdeutlichen, wird dieser noch einmal anhand eines 4-bit Zählers als Beispiel auf einer eigenen Seite detailierter aufzeigen.

Folgendes sind die 5 Hauptphasen einer ASIC-Entwicklung:

Phase 1: ASIC-Spezifikation

Phase 2: ASIC-Kodierung

Phase 3: ASIC-Synthese

Phase 4: ASIC-Layout

Phase 5: ASIC-Produktion

Da diese Seite nur als eine Übersicht der ASIC-Entwicklung dienen soll, sind insbesondere für die Hauptthemen ASIC-Kodierung, -Synthese und -Layout ausführlichere Seiten mit einem wesentlich

höheren Detailierungsgrad in Planung. Nebenbei sei noch bemerkt, daß die Phasen für eine ASIC-

Entwicklung die gleichen sind wie bei der Entwicklung von ASSP's oder eines Standardhalbleiters.

Phase 1: ASIC-Spezifikation

Zuallererst werden sämtliche Funktionen definiert und festgehalten, die der spätere Chip erfüllen soll.

Hierbei werden die Ideen der Entwickler herangezogen oder die Spezifikation erfolgt entsprechend bestimmter sogenannter 'Standards'. Sehr häufig ist es jedoch eine Mischung aus beidem, um einem

Produkt Vorteile gegenüber Konkurrenzprodukten zu geben.

Als Beispiel für einen Standard, den ein Chip erfüllen muß, kann man sich ein PC-Netzwerk vorstellen,

mit dem viele PCs miteinander kommunizieren. Ein Netzwerk-Standard gewährleistet, daß das zu entwickelnde ASIC - entsprechend des Standards - mit allen anderen Teilnehmern in diesem Netzwerk

kommunizieren kann, die natürlich ebenfalls dem gleichen Standard genügen müssen.

Neben der reinen funktionalen Beschreibung werden weitere physikalische Details in der ASIC- Spezifikation festgelegt, die letztenendes das Aussehen des Chips und seine Einsatzbedingungen bestimmen. Hierzu zählen:

- Gehäusetyp und Größe des Gehäuses

- Anzahl der Pins des Gehäuses

- Müssen u.U. Clocks aus einem Referenztakt erzeugt werden (PLL)

- Zuordnung jedes einzelnen Signals zu einem einzelnen Gehäuse-Pin

- Treibertyp und Treiberstärke (z.B. CMOS-Out, 3.3V, 9mA)

- Anzahl der Spannungsversorgungs-Pins und deren Pin-Positionen

- Einsatzbereich des ASIC's (Spannungsversorgung, zugelassener Temperaturbereich)

Phase 2: ASIC-Kodierung

Zur Kodierung von ASICs werden wie für Software passende `Programmiersprachen´ benutzt. Diese

beschreiben das Verhalten des Chips auf einer hohen abstrakten Ebene, die für den Menschen erfaßbar ist (programmierbar, lesbar). Eine Netzliste in `Reinformat´ ist nicht lesbar da man eine Unmenge von

Bauelementen mit jeweils rudimentären Funktionen überblicken müßte. Neben verschiedenen anderen Sprachen dominieren vor allem VHDL (VLSI Hardware Description Language) und Verilog die Entwicklung von ASICs.

Vergleichen kann man die Beziehung zwischen VHDL und der elektronischen Schaltung (auch Netzliste genannt) mit einer Programmiersprache (z.B. `C´) und dem prozessorabhängigen Maschinencode, der

aus dem C-Code mit dem Compiler compiliert wird.

Bevor ich auf die Synthese eingehe möchte hier nur kurz auf zwei wesentliche Designmodellierungen und Modellierungsstrategien verweisen, die bei der Erstellung des ASIC-Codes angewendet werden:

- Modellierung RTL (Register Transfer Level) und Behavior

- Strategie Top-Down oder Bottom-Up

Andere Strategien, die bei komplexen Systementwürfen angewendet werden, sind:

- Algorithmic Level Modeling (z.B. mit Matlab)

- System-Level Modeling / System-Level Design (SLD)

- Transaction-Level Modeling

Während der Kodierung und insbesondere am Ende dieser Phase, muß der VHDL-Code dahingehend untersucht werden, ob er auch wirklich die Funktionalität beinhaltet, die in der Spezifikation in Phase 1 festgelegt wurde. Dieser Schritt wird mit einem sogenannten Simulator durchgeführt, der eine Simulation des ASIC-Codes durchführt. Bei einem Vergleich mit einer PC Software, entspricht die Simulation dem Testlauf eines Programmes, bei dem alle Funktionen genau unter die Lupe genommen werden.

Testbench und Simulation

Das Verhalten nahezu jedes Chips, und damit auch das des ASIC-Codes, ist zunächst einmal passiv.

D.h. der Chip funktioniert oder `läuft´ nicht von alleine und seine Eingänge müssen erst von außen angesteuert werden, z.B. mit einem Takt und  einem Datenstrom. Hierbei müssen alle Eingangssignale des Codes mit wechselnden, aber definierten Werten belegt werden. Die

Ausgangssignale als auch der innere Zustand der Schaltung werden über den RTL-Code und seinem aktuellen inneren Zustand während der Simulation erzeugt. Als inneren Zustand bezeichnet man den Zustand von

Elementen, die nicht auf direktem Weg über eine Änderung der Ausgangssignale beobachtbar sind. Hierunter fallen im Wesentlichen die Zustände von FlipFlops und internen RAMs.

einem Datenstrom. Hierbei müssen alle Eingangssignale des Codes mit wechselnden, aber definierten Werten belegt werden. Die

Ausgangssignale als auch der innere Zustand der Schaltung werden über den RTL-Code und seinem aktuellen inneren Zustand während der Simulation erzeugt. Als inneren Zustand bezeichnet man den Zustand von

Elementen, die nicht auf direktem Weg über eine Änderung der Ausgangssignale beobachtbar sind. Hierunter fallen im Wesentlichen die Zustände von FlipFlops und internen RAMs.

Um die Außenwelt des ASICs nachzubilden wird um den ASIC-Code eine neue `Schale´ gelegt, die sogenannte Testbench. Diese erzeugt die Signalsequenzen auf die Chip-Eingänge (die sogenannten Pattern), was

entweder durch das Einlesen der Signalfolge aus einer bestehenden Datei oder durch eine algorithmische Beschreibung (Behavioral VHDL- Code)

erfolgen kann. Die Ausgangssignale werden im Idealfall durch die Testbench automatisch überprüft. Weiterhing ist es möglich, daß alle Signale des Chips über die gesamte Simulation hinweg in eine Datei

geschrieben werden, die später mauell oder mit anderen Software-Werkzeugen überprüft werden. Die Testbench selbst hat nach außen keine eigenen Ein- oder Ausgänge, nur die inneren Verbindungen zu dem ASIC-Code.

Natürlich ist die Testbench ebenfalls in VHDL oder Verilog geschrieben.

Phase 3: ASIC-Synthese

Am Anfang der Synthese steht die abstrakte Beschreibung des ASIC-Verhaltens in einem RTL-Code.

Mit der Synthese bzw. mit einem Synthese-Programm wird aus der RTL-Beschreibung eine Netzliste erzeugt, die genau das gleiche Verhalten hat, das der RTL-Code vorgibt und in der Simulation überprüft

worden ist.Die Synthese ist daher mit einem Compiliervorgang vergleichbar, der aus der z.B. aus einem C-Programm einen konkreten ausführbaren Maschinencode erzeugt.

|

- welche Eingangssignale sind Clocks und wie ist deren Frequenz

- welche Phasenlage haben die Clocks untereinander

- welche Phasenlage haben die Eingangssignale bezogen auf die Clocks

- in welchem Bereich darf die Phasenlage der Ausgangssignale bezogen auf die Clocks liegen

- welche internen Verbindungen sind zeitunkritisch

- wo liegen interne asynchrone Schnittstellen (Übergang von einer Clock auf eine Andere)

- wo werden interne Clocks erzeugt (z.B. Teiler) und was ist deren Frequenz und Phasenlage

- welche Eingangssignale müssen in einem bestimmten Betriebsmodus auf einen festen Wert (0 oder 1) geklemmt werden

- . . .

Der Vorgang der Synthese ist auf dieser Seite detaillierter beschrieben.

Design For Test

Im Anschluß an die Synthese des VHDL-Codes wird in die vorhandene Schaltung eine zusätzliche

Testlogik eingebaut, mit der man den Chip während der Produktion und nach dem Einlöten auf die Platine unabhängig von seiner Funktion testen kann. Man spricht bei dieser Logik von DFT (Design For

Test). Die Testlogik wird z.T. von den gleichen Softwarewerkzeugen eingebaut die vorher bei der eigentlichen Synthese benutzt wurden.

Phase 4: ASIC-Layout

Nach der ASIC-Synthese liegt nun eine Netzliste des ASICs vor. Eine Netzliste ist wie schon einmal erwähnt eine elektronische Schaltung, bestehend aus digitalen Bauelementen und deren elektrischen Verbindungen untereinander. Alles soll

sich am Ende auf dem Chip befinden, einem kleinen Stückchen Silizium, das auf seiner Oberfläche je nach Größe mal gerade einige mm2 bis z.Z. ca. 300 mm2 Fläche bietet. Nur um einmal die

Größenverhältnisse kurz aufzuwerfen: 100mm2 ist schon eine verhältnismäßig große Fläche, entspricht aber einer Kantenlänge von gerade mal 1 cm! Die Elemente der Schaltung und deren Verbindungen werden im Layoutprozeß

nacheinander in zwei Stufen bearbeitet:

bestehend aus digitalen Bauelementen und deren elektrischen Verbindungen untereinander. Alles soll

sich am Ende auf dem Chip befinden, einem kleinen Stückchen Silizium, das auf seiner Oberfläche je nach Größe mal gerade einige mm2 bis z.Z. ca. 300 mm2 Fläche bietet. Nur um einmal die

Größenverhältnisse kurz aufzuwerfen: 100mm2 ist schon eine verhältnismäßig große Fläche, entspricht aber einer Kantenlänge von gerade mal 1 cm! Die Elemente der Schaltung und deren Verbindungen werden im Layoutprozeß

nacheinander in zwei Stufen bearbeitet:

- Plazierung

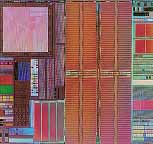

Bei der Plazierung werden alle Bauelemente auf der zur Verfügung stehenden Chipfläche - dem `Die´ (gesprochen `Dai´) - innerhalb des inneren Bereiches, der durch die IO-Buffer begrenzt wird, nach bestimmten Algorithmen verteilt. Die Position jedes einzelnen Elements der Core Logik (s. Bild) wird nach Möglichkeit so gewählt, daß die Verbindungswege zu den an ihm angeschlossenen Bauelementen möglichst kurz sind. Hierdurch wird einerseits erreicht, daß die Signallaufzeiten gering gehalten werden und andererseits, daß der Flächenverbrauch für die zu legenden Leitungen minimiert wird. Ein minimaler Flächenverbrauch bedeutet wiederum, daß man pro Flächeeinheit mehr Verbindungen unterbringen kann.

Die Positionierung und Reihenfolge der IO-Buffer, die über die Pads die Verbindungen des Chips von und nach außen darstellen, wird über das Chip Pinout bestimmt. Die IO-Buffer sind gegenüber den Elementen der Core Logik relativ groß, da sie einerseits einen großen Strom nach außen liefern können müssen (Output-Buffer) und andererseits großflächige Sicherheitsschaltungen enthalten, um die empfindliche Core Logik vor Spannungsspitzen von außen (EMV) schützen müssen. - Routing

Im Gegensatz zu den unveränderlichen Bauelementen hat eine elektrische Verbindung von A nach B einen Freiheitsgrad, nämlich den Weg. Dieser sollte wie oben schon erwähnt möglichst kurz sein. Häufig müssen jedoch Umwege in Kauf genommen werden, wenn der kürzeste Weg durch ein anderes Bauelement blockiert wird, oder bereits eine geroutete Verbindung den direkten Weg von A nach B blockiert. Wie kurz diese Wege sein müssen, oder besser gesagt, wie groß die Verzögerung (Ausbreitungsgeschwindigkeit des Signals auf diesem Weg) maximal sein darf, wird durch sogenannte Layout Constraints definiert, die das Zeitverhalten der Schaltung auf dem Die bestimmen.

(Weitere Details des Layouts befinden sich auf der Seite Chip Aufbau)

Nach Abschluß des Layouts wird die erzeugte Datenbasis vor der Freigabe zur ASIC-Produktion noch einmal gründlich unter die Lupe genommen. Hierbei finden verschiedene Strategien Verwendung um möglichst 100%ig sicher zu sein, daß die Layout-Ergebnisse sich genau so verhält wie gewünscht. Der neben der Funktionalität neue Aspekt, der durch das Layout in das Design hineinkommt, ist das reale Zeitverhalten (Timing). Die Funktionalität selber wird nicht durch den Layout-Prozeß verändert, obwohl an der Netzliste sehr häufig Manipulationen vorgenommen werden. Diese spielen sich jedoch ausschließlich auf der Ebene der Veränderung des Zeitverhaltens ab, wie z.B.

- schwache Treiber werden durch starke ersetzt

- neue Treiber werden in lange Verbindungen eingebaut

Stellt sich nach dem Test der Layout-Ergebnisse heraus, daß das gewünschte Zeitverhalten (welches durch die Constraints bestimmt wird) nicht erreicht werden kann, werden in einem zusätzlichen Prozeß

Korrekturen vorgenommen. Diese können neben der Verstärkung der Treiberleistung (s.o.) auch die Umplazierung von Elementen und deren Neuverdrahtung beinhalten.

Das reale Zeitverhalten der Schaltung wird aufgrund der

- Ausgangs-Treiberstärken der einzelnen Bauelemente ((Fan-Out)

- der Anzahl der jeweils angeschlossenen Eingänge ((Fan-In) anderer Bauelemente und

- der Längen der jeweiligen Verbindungen

aus den geometrischen Daten des Layouts berechnet und in einem sogenannten SDF-File (Standard Deal Format) abgelegt. Dieses kann in einer Gatelevel-Simulation und bei einer statischen Timinganalyse (STA, Static Timing Analysis) benutzt werden.

Eine weiterführende und vertiefende Beschreibung des Layouts ist bereits geplant. In dem Beispiel werden die einzelnen Bereiche des Dies näher beschrieben.

Phase 5: ASIC-Produktion

Aus dem Layout haben wir nun eine vollständige Netzliste und die Daten, um diese auf einer Chipfläche

zu plazieren. Alle bisher erzeugten Informationen liegen 'nur' in vielen z.T. sehr großen Dateien vor. Wie kommt nun diese Netzliste auf den realen Chip, den man dann auch endlich mal anfassen kann? Um es

noch einmal zu betonen: Bis hierhin ist wirklich alles nur im Computer passiert und alle Ergebnisse liegen als Datei auf vor!

Aus dem Layout wird neben den Plazierungs- und Verbindungsinformationen auch ein exaktes geometrisches Abbild des Chips erzeugt (GDS2- Format). Dieses darf man sich nicht als ein einzelnes Bild vorstellen. Vielmehr besteht dieses Abbild aus einer Anzahl übereinander angeordneter Maskendaten, mit dem man zunächst die Masken erzeugt. Anschließend wird mit den Masken der Wafer (den Chiprohling) in einem umfangreichen komplizierten physikalischen Prozeß nach und nach belichtet und die Schaltung so scheibchenweise aufgebaut (Diffusion). Der Wafer ist eine ca. 20cm-30cm große Siliziumscheibe, auf dem nach der Diffusion entsprechend der Chipgröße unterschiedlich viele Einzelchips angeordnet sind. Jeder einzelne Chip auf dem Wafer wird nach dem letzten Maskenprozeß auf seine Funktionsfähigkeit überprüft, wobei nicht funktionierende Chips markiert werden. Nach diesem sogenannten Wafertest werden die Chips auf dem Wafer längs ihrer Kanten geritzt und anschließend gebrochen. Jeder der unmarkierten Chips wird danach in ein Gehäuse gepackt. Bevor das Gehäuse gasdicht verschlossen wird, werden alle Signale des Chips über hauchdünne Golddrähte mit den Pins des Gehäuses verbunden. Dieser Vorgang wird Bonding genannt. Als letzter Schritt zur Fertigstellung des Chips wird noch einmal ein ausführlicher Test mit dem Package durchgeführt. Ist auch dieser ohne Fehler abgeschlossen, steht dem ASIC nun nichts mehr im Weg, in einem Handy, einem Drucker oder sonst einem elektronischen Gerät, für das das ASIC entwickelt worden ist, seine Arbeit zu verrichten.

Die allerersten Prototypen des Chips dienen dem ASIC-Kunden als Testmuster. Mit den sogenannten Engineering Samples wird das Endprodukt zunächst als Prototyp aufgebaut und auf Herz und Nieren getestet. Nach erfolgreichem Test der Engineering Samples wird normalerweise der Auftrag für die Massenproduktion des ASICs gegeben. Je nach Kunde und Endprodukt liegen die Stückzahlen im Bereich von einigen 100/Monat (z.B. ASICs für Meßelektronik) bis hin zu 100.000/Monat bei einigen Ausrüstern der Automobilindustrie.

[Home] [ASICs] [Selbstmanagement] [Inselmeer] [Spiele]

[Ich über mich] [Links] [SiteMap] [Disclaimer]